Evolution of server chip sets of the corporation of Intel

Evgenie Rudometov,

Victor Rudometov

rudometov@mail.ru

Basis of the motherboards used as a part of servers, computer networks controlling operation, YO special chipsets of system logic — chip sets are . The most complicated on the inner pattern the chips which are a part of such chip sets, carry out electrical, logical and informational link of high-powered processors with other ситемы components. The largest manufacturer of such chipsets is the corporation of Intel which for support of the server processors releases the appropriate specialised chip sets which architecture evolves together with development of solid-state technologies and the architecture of high-powered processors of the given group.

In the first part of article server chip sets of the corporation of Intel of last years have been described. These chipsets of system logic became a basis of the big number of high-powered systems. However it is necessary to mark, that all considered chip sets and the server solutions created on their basis, despite their functional saturation, concern already history. After release of server versions of processors with the architecture of Intel NetBurst the chip sets enumerated above were replaced by the bar of more perfect chipsets of system logic. Chip sets of the bar of Intel E75xx which ancestor is Intel E7500 became them. These sets in bolshej to a degree corresponded more to ample opportunities and the perfect architecture of server processors of a new generation.

Chip sets of Intel E7500/7501/7505

Before to estimate merits and demerits of server chip sets of the bar of Intel E75xx, it is expedient to remind basic performances of processors to concern Intel of Pentium Xeon.

The architecture of the processor of Intel Xeon is grounded on the same kernel, as Intel of Pentium 4.

Basic performances of this 32-bit (IA-32) kernels are following parametres:

· Hyperpipeline processing technique (Hyper Pipelined Technology). The long pipeline allows at the expense of some lowering of number of executable operations for clock tick considerably to increase clock rates. It as a whole increases the common proizvoditelnot,

· the Improved branch prediction (Improved Branch Prediction). As operations of cleaning and occupancy of the long pipeline demand rather big time, for high efficiency saving it is necessary to use the effective unit of a branch prediction,

· the Cache memory with tracing of 12 thousand instructions (12K micro-op trace cache). This special cache memory raises efficiency of processing of commands and data in the conditions of the long pipeline,

· the Mechanism of fast fulfilment (Rapid Execution Engine). Two arithmetic-logic units work on the doubled clock rate that allows to handle twice more than data for clock tick and effectively to load dinnyj the pipeline,

· the Improved cache memory of transmission (Advanced Transfer Cache). The Cache memory of the second level possesses not only a 256-bit wire, but is capable to handle data during each clock tick that provides high capacity of a subsystem of this type of memory,

· Hardware look-ahead sampling (Hardware Prefetch). At the expense of the effective mechanism of a prediction the processor provides preselection and loading of data from memory in a cache memory,

· Quad-speed (quad pumped) the processor bus. Capacity of the bus protsessra is increased four times at the expense of data transfer on quadruple, and addresses on doubled clock rate,

· Stream SIMD 2 (SSE2 extensions. The Command system is expanded at the expense of additional 144 additional instructions for processing of stream data,

· Processing technique Hyper-Threading. Provides productivity substantial increase by operation with multithreaded applications or in the multitask environments, supporting some program streams on each processor. It is reached at the expense of hardware support of two virtual processors in the presence of one physical.

For the architecture of processors of Intel Xeon support of dual-processor patterns is provided also. Besides, the size of the cache memory of the second level (cache memory L2) of released models of this group of processors makes 512 and 1024 Kbytes.

High value of cache memory L2 provide high efficiency and a store of resources for effective operation in the conditions of peak loads from the external and corporate applications demanding abbreviation of response time of system, increase in productivity, support bolshego numbers of users and a scalability high-scale. Thus clock rate of the upper models of processors of Intel Xeon reaches values of 3,06 and 3,2 GHz.

It is necessary to mark, that implementation of potential possibilities of high-powered processors of Intel Xeon substantially depends on an overall performance of chipsets of the system logic supporting these products.

So, the chipset of Intel E7500 represents the following step in development of processing technique and the architecture of chip sets of Intels created as a basis of high-powered server systems of a new generation. These chip sets are distinguished by wide functionality and the high efficiency, capable to open potential of server processors with very high clock rate of operation of inner patterns.

The first in the set, the chipset of Intel E7500 supports the dual-processor server platforms optimised for processors of Intel Xeon of microarchitecture of Intel NetBurst.

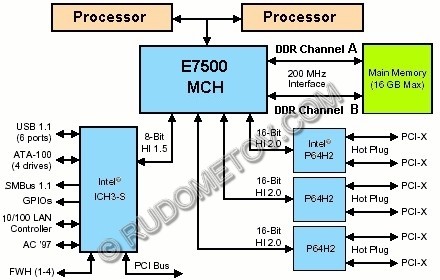

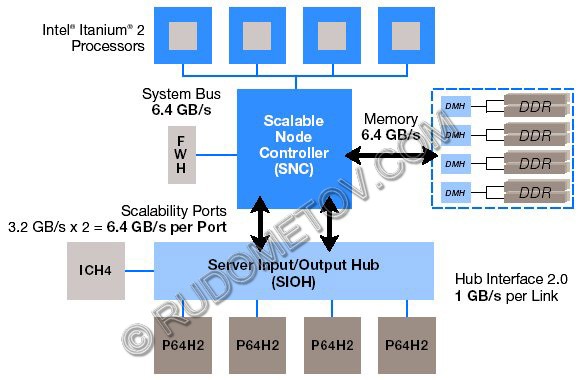

Fig. 4. Structure of the server created on the basis of a chip set of Intel E7500

The chip set of Intel E7500 is oriented to the architecture of servers in one or dual-processor patterns. Supports systems with processors of Intel Xeon. The given processors work with bus FSB of type QPB (Quad-Pumped Bus) which clock rate for the given chip set and appropriate processors makes 100 MHz. Considering features of algorithm and the interface of operation of the processor bus, clock rate of 100 MHz provides a transfer rate with frequency of 400 MHz, and addresses — 200 MHz (4X — for data and 2X — for the address). As a result peak capacity of the bus of the processor reaches in comparison with the predecessors created according to P6 architecture, is unprecedented high value of 3,2 Gbytes/with.

The chip set of Intel E7500, as well as its server predecessors, traditionally supports addressing of 36 bits, Symmetric Multiprocessing Protocol (SMP) for two processors, parity (Parity protection), an error correction (ECC), etc .

The chip set of Intel E7500 consists of three components — the controller-hub of memory of the chipset (Memory Controller Hub — MCH), the input/output controller-hub (I/O Controller Hub 3-S — ICH3-S), the controller-hub of 64-bit wire PCI/PCI-X (PCI/PCI-X 64-bit Hub 2 — P64H2).

MCH component is presented by a chip of Intel E7500 MCH containing resources of interfaces of operation with the processor, dynamic storage units, and also with chips of input/output and expansion cards — I/O Controller Hub and PCI/PCI-X 64-bit Hub 2

Built in a chip of Intel E7500 MCH the memory controller provides support: a two-channel functional mode of memory DDR SDRAM (Double Data Rate SDRAM — SDRAM with data transfer on lobbies and back edges of clock pulses of the bus of memory), memory modules DDR200, a maximum memory size — to 16 Gbytes, chips 64, 128, 256, 512 Mbit DDR SDRAM, the bus of memory of 144 bits, units of register memory ECC DDR. Here it is necessary to mark, that two-channel construction of a subsystem of memory provides a pass-band of 3,2 Gbytes/with that corresponds to a similar high metric of the processor bus. It provides a system coordination on informational streams and, as consequence, high prizvoditelnost systems.

Link with I/O Controller Hub 3-S components and PCI/PCI-X 64-bit Hub 2 is carried out with the help habovyh intervejsov (hub interface) — accordingly, HI 1.5 and HI 2.0. Thus key parametres habovogo interface HI 1.5 are 8 bits, 66 MHz (4x hub interface with a transfer rate of 256 Mb per second), interface HI 2.0 is characterised by following parametres: 16 bits, 66 MHz (4x hub interface with a transfer rate 1 Гбайт/c).

Р64Н2 component providing the interface with 64-bit expansion cards PCI/PCI-X, is presented by a specialised chip of Intel 82870P2. This component is jointed to controller-concentrator MCH through pointwise interconnection of interface Hub Interface 2.0. To chip MCH which is a part of chip set E7500, it is possible to hook up about three controllers P64H2. Thus capacity of each of them makes 1 Gbyte/with, that in the sum makes 3,2 Gbytes/with — a spare for the common capacity of all arrangements which are hooked up through the given variant of the interface. Each arrangement P64H2 contains two independent 64-bit interfaces PCI-X and two controllers PCI (on one on each interface PCI-X). Each 64-bit segment PCI-X supports some PCI-X plugs, providing high conducting interconnection for high-speed components. As an example of such arrangements it is possible to result adapters of Intel Gigabit Ethernet.

Handle of traditional rather slow peripheral devices is carried out by chip ICH3-S presented by a chip of Intel 82801CA. The given chip is jointed to controller-concentrator MCH through pointwise interconnection of interface Hub Interface 1.5. Controller-hub ICH3-S supports promptly becoming outdated interfaces of input/output. It is carried out by means of built in to specialised resources. The following concerns these resources the chips ICH3-S built in structure controllers: SMBus 2.0, PCI 2.2, two channels ATA/100 (Ultra DMA) for hooking up of arrangements IDE, six ports USB, a local area network 10/100M LAN, AC ’ 97 etc .

On the basis of the chipset of system logic of Intel E7500 the considerable quantity of servers and the powerful workstations, found wide application in different branches of an economic mechanism of many countries is created. However appearance of new models of processors demanded release of the adequate chip sets, capable to provide support of their functionality.

Simultaneously with release of processors of Intels Xeon created on the basis of kernel Prestonia (tehprotsess 0,13 microns), have been announced an appropriate set of system logic. This chip set earlier known as Plumas, is intended to support the given processors and represents further development of the architecture of a chip set of Intel E7500. The new chipset after its official declaration has received the name of Intel E7501.

So, the chip set of Intel E7501 actually represents an improved version of Intel E7500. Difference of Intel E7501 from the predecessor consists first of all in support the increased clock rates of the processor bus and dynamic storage units.

Really, if the chip set of Intel E7500 provides support of clock rate of the processor bus of 100 MHz (here it is necessary to remind, that the transmission frequency of data for clock rate of 100 MHz makes 400 MHz, addresses — 200 MHz) and DDR200 units, its successor — more perfect Intel E7501 — support of clock rates of 100 and 133 MHz (transmission frequencies of data — 400 and 533 MHz, addresses — 200 and 266 MHz) and memory modules DDR200 and DDR266.

All other parametres of the chipset of system logic of Intel E7501 practically coincide with similar parametres of its prototype to which is Intel E7500.

As well as its predecessor, a chip set of Intel E7501 consists of three components — the controller-hub of memory of the chipset (Memory Controller Hub — MCH), the input/output controller-hub (I/O Controller Hub 3-S — ICH3-S), the controller-hub of 64-bit wire PCI/PCI-X (PCI/PCI-X 64-bit Hub 2 — P64H2). Thus MCH component, is presented by a chip of Intel E7501, ICH3-S component — Intel chip 82801CA, and Р64Н2 — Intel chip 82870P2. Here it is necessary to pay attention, that two of three enumerated components coincide with the same, as in case of a chip set of Intel E7500. Difference consists only in the controller-concentrator of memory MCH which defines all advantages of a chip set of Intel E7501 over Intel E7500.

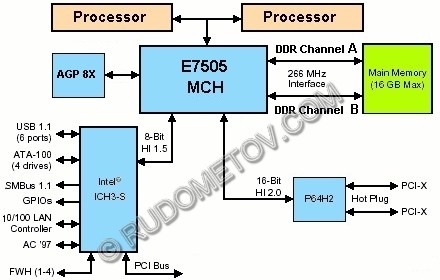

One more set concerning the set of Intel E75xx, the chip set of Intel E7505 is. This chip set before its official release was known under code name Placer.

Generally speaking, this chip set is not server, and is taken up a position as a basis for powerful workstations, as, for example, recently developed and released by Intel 875P. Nevertheless, on the basis of the chipset of system logic of Intel E7505 manufacturers release the products presented as server solutions. Similar variants were already realised on a basis before considered in the first part of article of sets, a part from which should were among the server. By the way, if on a site www.intel.ru the chip set of Intel E7505 is carried to group of sets for workstations on a site www.intel.com the same chip set is presented already and as server. It to some extent testifies to ample opportunities of the given specialised chipset of system logic which can be used in various systems: both in workstations, and in server solutions, than not primenuli to take advantage manufacturers of systems of high efficiency.

The chip set of Intel E7505 is oriented for systems of one or dual-processor patterns. The given chip set supports to two processors of Intel Xeon (kernel Prestonia), the processor bus with clock rates of 133 and 100 MHz (transmission frequencies of data — 533 and 400 MHz, addresses — 266 and 200 MHz) and a two-channel pattern of a subsystem of dynamic storage DDR266 or DDR200.

Fig. 5. Structure of the server created on the basis of a chip set of Intel E7505

Unlike server sets of system logic of Intel E7500 and Intel E7501, instead of chip ICH3-S which is responsible for input/output, as a part of a chip set of Intel E7505 uses traditional ICH4 component. Besides, in MCH component architecture standard port AGP for desktop computers 8Х uses nonconventional for server solutions, but , and in instead of three chips P64H2 as a part of a chip set one chip of the given type uses.

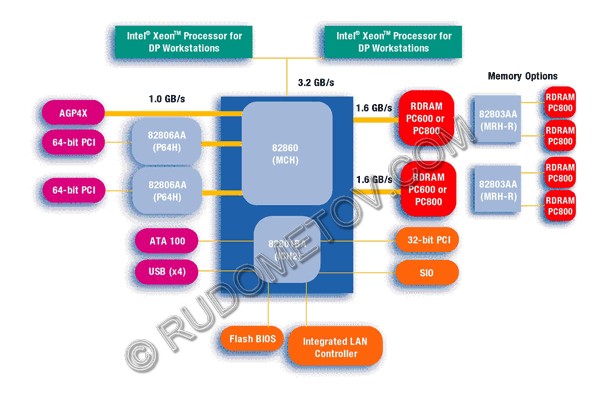

For other example of usage as a basis of server systems of chipsets of the system logic oriented to the market of powerful workstations, can be Intel 860.

The chipset of Intel 860 is developed specially for high-powered multiprocessing systems. Together with processors of Intel Xeon this chipset provides productivity and scalability high level. Supports to two processors.

The chipset of Intel 860 includes two main components: the controller-hub of memory 82860 (MCH) and the controller-concentrator of input/output 82801 (ICH2).

Fig. 6. Structure of the server created on the basis of a chip set of Intel 860

The memory controller-hub supports the processor bus with clock rate of 100 MHz (frequency pereachi the given 400 MHz) and has high-powered dual channels for memory RDRAM (4 RIMM units, PC800/600, ECC), and also provides possibilities of hooking up of peripherals, including hooking up through two high-speed 64-bit PCI-buses working on frequency of 66 MHz. Besides, it provides support of graphics systems with AGP 4X.

The input/output controller-hub is linked to component MCH the local bus, characteristic for the bar of chip sets of Intel 8хх. He instal a direct data link with graphics system and memory, allowing to accelerate access to peripherals, and provides functions and a pass-band, necessary for high-powered computer solutions. Supports 32-bit controller PCI, interface Ultra ATA/100, the integrated controller of a local area network and two doubled controllers USB, providing data transfer on four ports. Support of 6 digital sound channels concerns other refinements of the controller-hub for reaching of volume sounding and controller AC support ' 97.

Besides high efficiency, the chipset of Intel 860 provides scalability high levels. Two additional can be hooked up to its main components: 64-bit controller-hub PCI 82806AA (P64H) and the hub-repeater of memory RDRAM 82803AA (MRH-R).

Chip P64H supports 64-bit wire PCI with frequency of 33 or 66 MHz. This chip is hooked up directly to controller-concentrator MCH according to the improved hub-architecture of Intel, and provides the selected high-speed channel of input/output.

Chip MRH-R is intended for systems with increased requirements to memory capacity RDRAM. This chip provides conversion of each channel of memory to two, effectively increasing maximum size of supported memory: to 8 RIMM units.

By the original simplified variant of Intel 860 the chip set of Intel 850 which also is calculated for systems with memory RDRAM in its two-channel pattern can be considered. By the way, this pattern reminds well-known Intels 820 and Intels 840 developed for processors IntelPentium III and IntelPentium III Xeon. However unlike the specified chip sets chipsets of Intel 860 and Intels 850 provide the solutions balanced concerning informational streams thanks to high capacity of processor bus FSB of type QPB. As consequence of high potential possibilities, the chip set of Intel 850 which have been taken up a position as a basis of workstations and powerful desktop computers, some corporations used in the server solutions. However, these solutions have not got the big popularity for users.

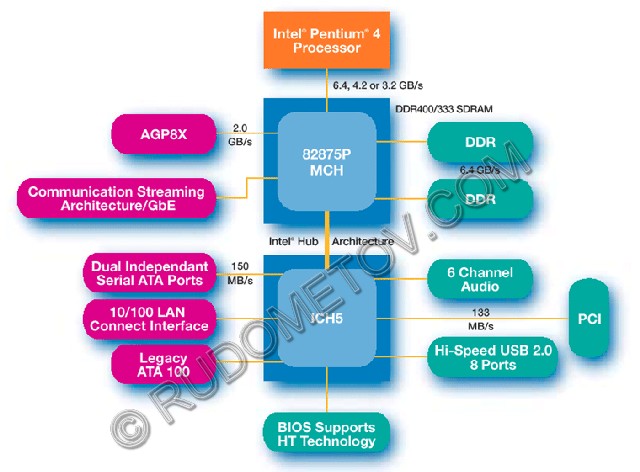

One more challenger for a role of the chipset of system logic for server systems is more modern in comparison with Intel 860 chip set of Intel 875P, oriented, generally speaking, on the market of workstations and powerful desktop computers. On the basis of this chip set some manufacturers have released server systems of initial level with processors IntelPentium 4. So, for example, Intel corporation, offers Intel Entry Server Board S875WP1-E. However, in it there is nothing surprising as to numerous users motherboard IntelServer Board S845WD1-E created on the basis of a chip set of Intel 845PE with an one-channel pattern traditional until recently of dynamic storage is known, conceding on possibilities to more powerful Intel 875P.

Intel chip set 875P, known earlier as Canterwood, is oriented to creation of workstations and high-powered desktop personal computers. Supports processors of Intel of Pentium 4 with processing technique Hyper-Threading, 0,13 microns created on processing technique hooked up through Socket 478 plug and working with bus FSB of type QPB (Quad-Pumped Bus). Clock rate can make 100, 133 or 200 MHz.

Built in Intel chip 82875P (MCH) the controller of processor bus FSB of type QPB supports the bus with clock rate of 200/133/100 MHz that provides data transfer on frequencies according to 800/533/400 MHz.

The memory controller provides support: two and one-channel functional modes of dynamic storage DDR SDRAM with DDR400/333/266 units, a maximum memory size — to 4 Gbytes, chips 128, 256, 512 Mbit DDR SDRAM, units both with ECC, and without ECC. In patterns with support ECC in a two-channel mode the bus of 144 bits, without support ECC — 128 bits uses .

For a synchronous functional mode of units of dynamic storage DDR400 and frequency of the bus of 800 MHz probably usage of the mode providing raised productivity of a subsystem of memory — processing technique of Intel PAT (Performance Acceleration Technology). In this mode the delays linked to synchronisation are minimised.

The built in controller of a drawing supports one arrangement 0,8/1,5 In AGP 3.0, supporting mode AGP 8X.

From features of hub MCH it is necessary to mark, that in its architecture it is realised the special interface (bus CSA), allowing to realise Gigabit Ethernet. Carrying over of these resources from chip ICH in MCH speaks insufficient capacity of the local bus jointing hubs MCH and ICH.

Handle of computer peripheral devices is carried out by the second component of a chip set — ICH5 which is presented by Intel chip 82801ЕB. This chip enters into a base set of a chip set i875P.

The built in resources of a chip of handle of peripheral devices of a base set support: two channels IDE with support ATA 33/66/100 (to four arrangements IDE), two ports Serial ATA 150, six ports USB 2.0, six PCI (32 bits/33 of MHz), LPC (Low Pin Count), AC ' 97 with support of three codecs of the audiochannels, the integrated controller 10/100 Base-TX Ethernet, SMBas, ACPI 2.0, and also other resources and functions.

Except Intel 82801ЕB, usage of the expanded version of hub ICH5 — ICH5R is possible . This expanded variant is presented by Intel chip 82801ЕR. It differs from the predecessor presence of function RAID of level 0 — processing technique of Intel RAID 0.

Fig. 7. Structure of the computer created on the basis of a chip set of Intel 875P

The resulted sets of the set of Intel E75xx, and also chip sets of Intel 860 and Intel 875, are intended for processors of Intel Xeon of the architecture of Intel NetBurst, however topovymi models (High-End) server processors of this corporation are high-powered 64-bit (IA-64) processors of Intel Itanium and Intel Itanium 2.

The choice of a processor platform will depend not only on applications and the operating system, but also and from applied value and productivity of these two architectures. And they depend on the used chipsets of the system logic supporting given processors. According to differences of the bar of Intel Itanium from traditional 32-bit models, release of 64-bit processors was accompanied by the announcement of chip sets supporting these products.

Chip sets for Intel Itanium / Itanium 2

Basic performances of processors of the bar of Intel Itanium:

· Are created on the basis of EPIC architecture (Explicitly Parallel Instruction Computing),

· 128 general-purpose registers, 128 registers for floating-point operations, 64 predicative registers, 8 registers of branching,

· Possibility of creation of patterns as the manufacturer has declared, from 512 processors,

· 64-bit addressing and high capacity of memory,

· the Advanced architecture of complete automatic checking Machine Check Architecture (MCA) with expanded usage of a code of error correction ECC,

· Support by HP-UX operating systems, Linux, Windows Server 2003.

The set of system logic of Intel has been developed for support of 64-bit processors of Intel Itanium 460GX. This chip set is the first chipset of system logic which are carrying out support of 64-bit microarchitecture of the set of processors of Intel Itanium. The given multiconfiguration chipset is optimised for 1, 2, 3 and 4-processor server systems and dual-processor workstations on the basis of processors of Intel Itanium.

Intel chipset 460GX supports the interface of the controller of memory and appropriate bridges of buses PCI, AGP 4X and other standard buses of arrangements of input/output.

The controller the memory hub is presented by a chip 82461GX or 82462GX. Carries out support of memory PC100 SDRAM in size to 64 Gbytes and to the video schedule of standard AGP 4X/2X,

The controller of input/output IFB carries out support PCI 2.2, ATA33, 2 ports USB, built in resources AC ’ 97, etc .

The extension of a subsystem of input/output is provided: Bridge PCI eXpander (PXB), high-speed bridge PCI eXpander (WXB).

As is known, development of the architecture of Intel Itanium has found the continuation in the bar of processors of Intel Itanium 2. Processors of Intel Itanium 2 are binary-compatible with the existing software created for the processor of Intel Itanium that provides eligibility of developments system and applied ON.

The microarchitecture of the processor of Intel Itanium 2 provides fast access to the integrated cache memory, high capacity at information interchange between the central processor unit and system memory and possesses the considerable computing resources accelerating performance of commands and raising the common productivity of system. In the architecture of Intel Itanium 2 the 124-bit wire (earlier — 64 bits) is used , providing data transfer on frequency of 400 MHz (earlier — 256 MHz), that has provided three times the big capacity of the bus of the processor, than in case of the predecessor.

Some models of the processor of Intel Itanium of 2 variants MP (Multi-Processor) and DP (Dual Processor) with clock rates 1,5, 1,4, 1,3, 1,0 GHz are released. The three-level cache memory of the given models is characterised by following values of informational size: L1 — 32 Kbytes (commands and data), L2 — 256 Kbytes and L3, accordingly, — 6, 4, 3, 1,5 Mb. Thus the model with clock rate of 1,4 GHz exists in two variants of size of cache memory L3: 4 and 1,5 Mb.

The upper model of the processor of Intel Itanium 2 with size of the cache memory of the third level of 6 Mb (kernel Madison, tehprotsess 0,13 microns) is hardware and program compatible to the first version of the processor of Intel Itanium 2 (kernel McKinley, 0,18 microns). It provides protection of investments of original equipment manufacturers and end users. Besides, this model is binary-compatible with existing programs for the architecture of Intel Itanium (Merced, 0,18 microns) and can provide rise of productivity to 30 %-50 % and more in comparison with the predecessor.

The special set of the system logic which has received the name of Intel E8870 has been developed for support of new processors (Intel 870).

Inte E8870 chipset is the first in the architecture of a new generation the chipset specially developed for satisfaction of requirements of two-and four-processor server platforms of a highest level. The chipset of Intel E8870 optimised for the processor of Intel Itanium 2, provides productivity and scalability high level, and also preventing, detection and an error-checking.

Fig. 8. Structure of the server created on the basis of a chip set of Intel 8870

Basic performances of a chip set of Intel 8870 concern:

· 400 MHz, the 128-bit system bus that provides a data transfer high speed — to 6,4 Gbytes/with,

· very much great volume of dynamic storage — hub DMH gives in the sum 32 plugs for memory installation on each processor site, maximum size — 128 Gbytes (with 4 DDR Memory Hubs),

· Two vysokopropusknyh scaled port,

· Four interconnections of interface Hub Interface 2.0 with capacity of 1 Gbytes/with on each interconnection that allows to use to four 64-bit controllers PCI/PCI-X (P64H2) with interface HI 2.0,

· the Mechanism of preloading of data and the built in cache memory of an input/output system,

· Support of high-powered bridge PCI/PCI-X — support of all arrangements of input/output PCI/PCI-X I/O, starting from become outdated PCI and ending high-powered PCI-X on frequency of 133 MHz (each controller P64H2 contains two independent 64-bit channels PCI-X with maximum frequency of 133 MHz).

Besides, the combination of such characteristics as "hot-plug units for the processor and memory, detection and an error correction, restoring of glitches of arrangements of memory (MDFR), the backup paths of input/output and conducting log of writing of errors, gives more reliable platform, reduces time of idle times for repair and provides integrity of data transfer on all interconnections and buses.

The chipset of Intel E8870 consists of following main components: Intel E8870IO (SIOH), Intel E8870 (SNC), Intel E8870DH (DMH), Intel 82870P2 PCI/PCI-X (P64H2), Intel 82801DB (ICH4).

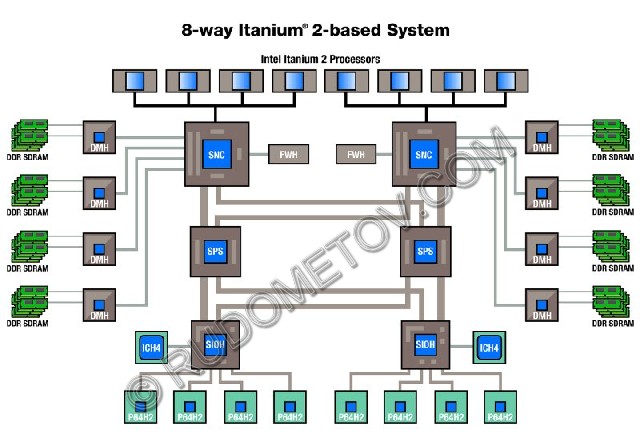

Usage of Intel E8870SP — E8870SP Scalability Port Switch (SPS), allows to expand possibilities of a chip set of Intel E8870 and to create systems with vosemju processors of Intel Itanium.

Fig. 9. Server structure c vosemju processors of Intel Itanium 2, created on the basis of a chip set of Intel 8870

Servers on the basis of processors of Intel Itanium 2 represent the powerful, cost effective and flexible computing platforms capable both to satisfy current requirements of firm, and to form base for the extension in the future. Processors of Intel Itanium 2 with the cache memory of the third level of 6 Mb form base for the powerful server solutions meeting high requirements of the big databases. Rather recently created powerful processors of Intel Itanium 2 with high clock rate and the cache memory of considerable size allow to create the big clusters of dual-processor systems for high-powered calculations and modern network applications. Systems on the basis of new low-tension processors of Intel Itanium 2 possess the raised density of components, saving high efficiency of processors of Intel Itanium with clock rate of 1 GHz and demand much less than electrical power, than traditional versions: 62 W against 130 W of the upper models. It allows to create the compact and economic multiprocessor solutions demanding less severe constraint maintenance.

In conclusion of the given short browse it is necessary to remind, that process of perfection of processors and development of the new architectures, carried out by experts of the corporation of Intel, certainly it is not completed. Moreover, it proceeds with escalating rate and there is no underplate to consider, that this process will sometime stop or, at least, will at least be decelerated. In many respects it is promoted by the considerable financial resources put in development of the newest computer processing techniques. That is why the corporation of Intel with an enviable regularity refreshes bars of the processors. Approximate periods of new 32 architectures and 64-bit server processors created on newest of 90 nanometers of processing technique are already declared .

And new processors, as always, will demand new chip sets which become a basis of even more efficient systems possessing wider set of functionality. Therefore already in the near future we are expected by the new even more efficient and functionally sated sets of system logic intended for server systems, the newest computer ideas being an original concentrate and processing techniques which after approbatsii both developments in servers and workstations become property and other sectors of the computer market.

In article substances of the corporation of Intel are used

Article is published in log Byte (http://www.bytemag.ru).

English

English Russian

Russian German

German