Server chip sets ServerWorks

Evgenie Rudometov

authors@rudometov.com

In the computer market of servers and workstations well-known also have got popularity chipsets of the system logic ServerWorks oriented to multiprocessing systems. The structure of these sets includes the various components, allowing to create systems of a different pattern depending on a functionality and cost

Multiplexing of computing circuits for the purpose of sharing of their shared resources demands effective server solutions. Thus, the more power of a used server, also is more critical its mission, the more it requires the functions providing dependability, availability and use reliability, — RAS (Reliability, Availability and Serviceability). All it is provided with the optimal architecture of the systems which basis is made by chipsets of system logic — the chip sets, servers in many respects defining functionality.

Release of the popular chip sets which have received name ServerWorks, company Broadcom Corporation which in 2001 for 957 million US dollars has gained the corporation with the name with the same name with chip sets is engaged. The products created by engineers attached ServerWorks, and also own implementators on the basis of usage of perspective computer and newest solid-state technologies, company Broadcom Corporation helps designers of reliable, efficient systems to solve their numerous problems.

ServerWorks architecture

The logic of the servers which central link are chip sets, defines number of processors which the system can use. Productivity and dependability of operation depend on it. Applied chip sets substantially define a pass-band, size and dependability of a subsystem of memory, along with number and speed of operation of used maps of the extension. Besides, the chips which are a part of chip sets, define efficiency of functioning of subsystems of input/output of the information. Thus the architecture of the chip sets defining to the logician of system, plays a key role in definition of operation of a server. Badly developed logic can strangle system operation.

Traditionally basis of modern chip sets are two components. The first is presented by the chip which has received name North Bridge. This component links the central processor unit and if it is some of them all processors with a dynamic storage subsystem. In addition to it, the given component inspects operation of maps of the extension which are hooked up to North Bridge, and also keeps in contact with the second component of a chip set.

This component is the chip named South Bridge. It by means of the built in resources and external units provides the control over operation of the big number of rather slow peripheral devices.

It is necessary to mark, that sharing of chip sets on components allows to develop specialised chips. It provides effective problem solving at the expense of a combination of components.

It is necessary to add, that in multiprocessing systems of one of basic functions of chip North Bridge coordination of mutual operation of the array of central processor units and sharing of their resources is. The numerous buses which are a part of the architecture of the computer system and streams of the information handled with their help concern these resources, by the way.

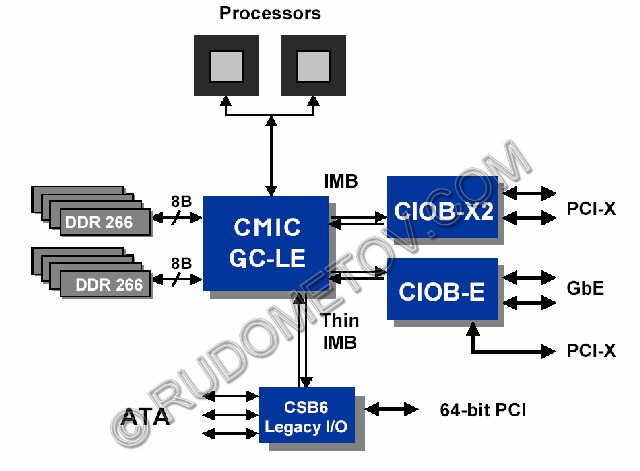

Fig. 1. Simplified patterns of the server created on the basis of chip set ServerWorksGrand Champion LE System I/O

As an example of such solution in a Fig. 1 the simplified structure of a pattern of the server created on the basis of one of chip sets ServerWorks — Grand Champion LE System I/O is presented . This chip set is the widespread chipset of system logic for sector of the solutions oriented to usage of processors of corporation of Intel.

Basis of the architecture of it and other chip sets are the traditional North Bridge components, carrying name Champion Memory and I/O Controller (CMIC), and South Bridge — Open South Bridge (OSB) or Champion South Bridge (CSB). The specified components added with special units, are traditional for high-powered computer complexes.

As follows from features of the resulted chip set ServerWorks, used processors of Intel, and also their architecture of Intel NetBurst, capacity of the processor bus on maximum clock rate makes 4,2 Gbytes/with. For support of maximum loading of this bus the two-channel pattern of a subsystem of the dynamic storage constructed on the basis of DDR SDRAM units — DDR200/DDR266, satisfying specifications PC1600/PC2100 is required .

For support of correct operation of a two-channel subsystem of dynamic storage units are installed by steams in the slots which number can to reach for the specified chip set of eight, and a maximum memory size at usage of 2 Gbytes of units — to 16 Gbytes. Rise of dependability of operation is provided with application of processing technique ECC providing detection and an error-checking. In addition, function Chipkill providing restoring of system in case of mortality of chips of memory uses, and also to switch memory banks, substituting their backup.

As to other features of the architecture of system it is necessary to mark the components controlling expansion cards. As an example it is possible to result special bridges of input/output (I/O bridges), carrying names CIOB-X2 and CIOBE.

The CIOB-X2 component (Champion I/O Bridge for PCI-X) controls two controllers PCI-X, each of which provides a stream of the information with a transfer rate to 1 Gbit/with. It is necessary to mark, that specification PCI-X 2.0 provides a transfer rate 2 or 4 Gbit/with. But even at 1 About the common stream reaches 2 Gbit/with. For support of such stream from CIOB-X2 in system North Bridge component special bus Inter-Module Bus (IMB) with capacity to 3,2 is Gbit/with.

The CIOB-E component (Champion I/O Ethernet Bridge for PCI-X) controls two controllers Gigabit Ethernet (GbE), and also PCI-X.

Except the specified units of the resulted pattern of system, it is necessary to mark a chip fulfilling functions South Bridge components. It can be, for example, CSB6 (Champion South Bridge, version 6). This component provides system loading, processing of I/O-interruptions, and also support of 64-bit wire PCI, cheryreh ports USB, three interfaces of drives ATA, etc .

It is necessary to add, that for systems of a different pattern the different components, differing are offered by functionality and the price also. Among them chip North Bridge and South Bridge, and also memory controllers, input/output bridges, controllers Serial ATA. The part from them is presented on a firm site of company Broadcom Corporation. These komponety cover a wide band of solutions from processors with the architecture of Intel P6 to Intel NetBurst.

So, chip sets ServerWorks, intended for different patterns and different processors in evolutionary razvitiii.

Chips North Bridge

LE

Champion Entry Dual Processor System I/O Platform

Chip North Bridge of chip set Champion LE System I/O is oriented to dual-processor platforms of initial level (LE — Low End). Supports to two processors of Intel of Pentium III Xeon (P6 architecture) with bus FSB of 100 MHz or 133 MHz. Controls streams of the information from processors and to them, and also dynamic storage and the peripheral devices which are responsible for input/output. The controller of a subsystem of memory PC100/PC133, the interface of 64 bits/66 of MHz PCI, and also the interface of 32 bits/33 of MHz PCI is integrated into structure , providing, in particular, hooking up to chip South Bridge. Supports to 4 Gbytes of total amount of units of dynamic storage with a pass-band to 1.1 Gbytes/with. Support of functions RAS (Reliability Availability and Serviceability) — cleaning of memory and ECC is provided .

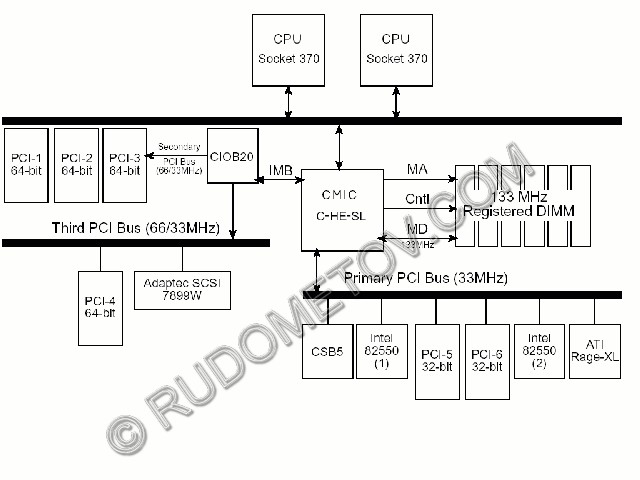

HE-SL

Champion Volume Dual Processor System I/O Platform

Chip North Bridge of chip set Champion HE-SL System I/O is oriented to dual-processor platforms of wide application. Supports to two processors of Intel of Pentium III Xeon (P6 architecture) with bus FSB of 100 MHz or 133 MHz. Controls streams of the information from processors and to them, and also dynamic storage and the peripheral devices which are responsible for input/output. The two-channel controller of a subsystem of memory PC100/PC133, the controller of the bus of the internal interface of input/output is integrated into structure of given chip HE-SL — Inter Module Bus (IMB) I/O interface, and also the interface of 32 bits/33 of MHz PCI, providing, in particular, hooking up to chip South Bridge. Specified chip North Bridge is capable to support to 6 Gbytes of dynamic storage with a pass-band to 2.1 Gbytes/with. Support of functions RAS (Reliability Availability and Serviceability) — cleaning of memory and ECC is realised . Created in the architecture of HE-SL component channel IMB provides for input/conclusion a pass-band to 1 Gbytes/with and admits usage of two buses of 64 bits/66 of MHz PCI.

Fig. 2. One of variants of a pattern of the server created on the basis of chip set ServerWorks ChampionHE-SL System I/O

HE

Champion Enterprise Quad Processor System I/O Platform

Chip North Bridge of chip set Champion HE System I/O is oriented to four-processor high-powered platforms (HE — High End). Supports to four processors of Intel of Pentium III Xeon (P6 architecture) with bus FSB of 100 MHz. Controls streams of the information from processors and to them, and also dynamic storage and the peripheral devices which are responsible for input/output. The fourline controller of a subsystem of memory PC100/PC133, the controller of the bus of the internal interface of input/output is integrated into structure of given chip HE — Inter Module Bus (IMB) I/O interface, and also the interface of 32 bits/33 of MHz PCI, providing, in particular, hooking up to chip South Bridge. Specified chip North Bridge is capable to support to 16 Gbytes of dynamic storage with a pass-band to 4.2 Gbytes/with. Support of functions RAS (Reliability Availability and Serviceability) — cleaning of memory and ECC is realised . Created in the architecture of HE-SL component channel IMB provides for input/conclusion a pass-band to 1 Gbytes/with and admits usage of two buses of 64 bits/66 of MHz PCI.

GC-WS

Grand Champion Volume Workstation Dual Processor System I/O Platform

Chip North Bridge of chip set Grand Champion WS (GC-WS) System I/O provides support AGP 8Х and is oriented to dual-processor platforms for workstations.

Supports to two processors of Intel Xeon (the architecture of Intel NetBurst) with buses FSB of 133 MHz providing a transfer rate with frequency of 533 MHz. Controls streams of the information from processors and to them, and also dynamic storage, a graphics subsystem and the peripheral devices which are responsible for input/output.

The two-channel controller of a subsystem of memory DDR266, two controllers of the bus of the internal interface of input/output is integrated into structure of given chip GC-WS — Inter Module Bus (IMB) I/O interface, and also one controller Thin-IMB I/O interface through which is carried out hooking up to chip South Bridge. Specified chip North Bridge is capable to support to 16 Gbytes of dynamic storage with a pass-band to 4.2 Gbytes/with. Support of functions RAS (Reliability Availability and Serviceability), providing support of algorithm of 128 bits ECC, processing techniques Chipkill and Spare Memory is realised . Double channels IMB created in GC-WS architecture provide everyone for input/conclusion a pass-band to 3.2 Gbit/with.

GC-SL

Grand Champion Entry Dual Processor System I/O Platform

Chip North Bridge of chip set Grand Champion SL (GC-SL) System I/O is oriented to dual-processor server platforms of initial level.

Supports to two processors of Intel Xeon (the architecture of Intel NetBurst) with buses FSB of 100 and 133 MHz providing a transfer rate with frequencies of 400 and 533 MHz. Controls streams of the information from processors and to them, and also dynamic storage and the peripheral devices which are responsible for input/output.

The controller of a subsystem of memory DDR200/DDR266, one controller of the bus of the internal interface of input/output is integrated into structure of given chip GC-SL — Inter Module Bus (IMB) I/O interface, and also one controller Thin-IMB I/O interface through which is carried out hooking up to chip South Bridge.

Specified chip North Bridge is capable to support to 4 Gbytes of dynamic storage with a pass-band to 2.1 Gbytes/with.

Support of functions RAS (Reliability Availability and Serviceability), providing support of algorithm of 128 bits ECC and processing techniques Spare Memory is realised .

Channel IMB provides for input/conclusion a pass-band to 3.2 Gbit/with.

GC-LE

Grand Champion Volume Dual Processor System I/O Platform

Chip North Bridge of chip set Grand Champion LE (GC-LE) System I/O is oriented to dual-processor server platforms.

Supports to two processors of Intel Xeon (the architecture of Intel NetBurst) with buses FSB of 100 and 133 MHz providing a transfer rate with frequencies of 400 and 533 MHz. Controls streams of the information from processors and to them, and also dynamic storage and the peripheral devices which are responsible for input/output.

The two-channel controller of a subsystem of memory DDR200/DDR266, two controllers of the bus of the internal interface of input/output is integrated into structure of given chip GC-LE — Inter Module Bus (IMB) I/O interface, and also one controller Thin-IMB I/O interface through which is carried out link with chip South Bridge.

Specified chip North Bridge is capable to support to 16 Gbytes of dynamic storage with a pass-band to 4.2 Gbytes/with.

Support of functions RAS (Reliability Availability and Serviceability), providing support of algorithm of 128 bits ECC, processing techniques Chipkill and Spare Memory is realised .

GC-LE components created in the architecture double channels IMB provide everyone for input/conclusion a pass-band to 3.2 Gbit/with.

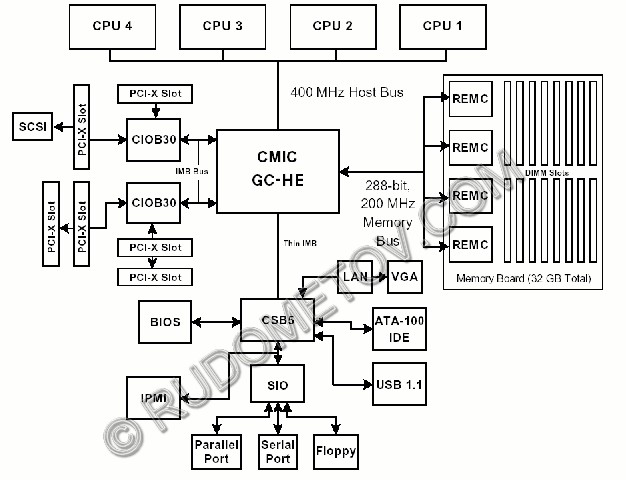

GC-HE

Grand Champion Enterprise Quad Processor System I/O Platform

Chip North Bridge of chip set Champion HE System I/O is oriented to four-processor high-powered platforms.

Supports to four processors of Intel of Pentium 4 Xeon with buses FSB 100 providing a transfer rate with frequencies of 400 MHz. Controls streams of the information from processors and to them, and also dynamic storage and the peripheral devices which are responsible for input/output.

The fourline controller of a subsystem of memory DDR200, three controllers of the bus of the internal interface of input/output is integrated into structure of given chip GC-WS — Inter Module Bus (IMB) I/O interface, and also one controller Thin-IMB I/O interface through which is carried out link with chip South Bridge.

Specified chip North Bridge is capable to support to 64 Gbytes of dynamic storage with a pass-band to 6.4 Gbytes/with.

Support of functions RAS (Reliability Availability and Serviceability), providing support of algorithm of 128 bits ECC, processing techniques Chipkill, Spare Memory, Memory Mirroring and Hot Plug Memory Card is realised .

North Bridge components created in the architecture three channels IMB provide for input/conclusion a pass-band to 1.6 About everyone.

Fig. 3. One of variants of a pattern of the server created on the basis of chip set ServerWorks GrandChampion GE-HE System I/O

Chips South Bridge

OSB4

Champion Compatible System I/O South Bridge

Chip Open South Bridge 4 (OSB4) System I/O Bridge fulfils functions of system South Bridge component. This chip is the multifunctional unit supporting Plug and Play.

Controls inbox and the outgoing streams of the information generated by units ISA, USB, ATA, SMBus, SuperI/O. Such resources as an interrupt controller compatible with 8259, General Purpose I/O, I/O APIC, controller DMA compatible with 8237, etc. Besides, in structure of chip OSB4 controls for power supply are built in are integrated Into the given chip: ACPI, Clock Throttling, the timers/counters compatible to a chip 8254, function of inaktivatsii/turn off of power supplies, etc.

CSB5

Champion and Grand Champion Compatible System I/O South Bridge

Chip Champion South Bridge 5 (CSB5) System I/O Bridge fulfils South Bridge component functions. This chip is the multifunctional unit supporting Plug and Play.

Is the bridge between PCI and Low Pin Count (LPC), supports double channel ATA/100, 4 ports USB 1.1, the security guard (passwords and system protection). Controls inbox and the outgoing streams of the information generated by units PCI, USB, ATA, SMBus, LPC and SuperI/O.

Resources ATA/100 are integrated into structure of the given chip, USB, an interrupt controller compatible with 8259, General Purpose I/O, I/O APIC and controller DMA compatible with 8237.

Link with North Bridge is provided by resources of interface Thin IMB used as a part of chips North Bridge for platforms with the architecture of Pentium 4 and compatible to interface resources, used in North Bridge for the architecture of Pentium III.

Controls for power supply are built in structure of chip OSB5: ACPI, Clock Throttling, the timers/counters compatible to a chip 8254, resources inaktivatsii and power supplies turns off, etc .

CSB6

Grand Champion Compatible System I/O South Bridge

Chip Champion South Bridge 6 (CSB6) System I/O Bridge fulfils South Bridge component functions. This chip is the multifunctional unit supporting Plug and Play.

Controls inbox and the outgoing streams of the information generated by units PCI, USB, ATA, SMBus, LPC and SuperI/O, supports three channels ATA/100, 4 ports USB 1.1, the security guard (passwords and system protection).

Resources ATA/100 are integrated into structure of the given chip, an interrupt controller compatible with 8259, General Purpose I/O, I/O APIC and controller DMA compatible with 8237.

Besides, controls for power supply which concern ACPI are built in structure of chip OSB6, Clock Throttling, the timers/counters compatible to a chip 8254, resources of inaktivatsii/turn off of power supplies Are, etc. realised some server resources, for example, Watchdog timer, support NVRAM, LCD and Keypad.

Memory controllers

REMC

Grand Champion System I/O Memory Controller

The chip of the controller of memory Grand Champion Reliability Enhanced Memory Controller (REMC) supports 2-Way and 4-Way patterns with memory alternation. Four chips REMC use in 4-Way patterns of the interleaved memory for simplification of multiplexing and data buffering while fifth chip REMC uses in Address Path for generation of plural copies of the address and check signals.

MADP

Champion System I/O Memory Controller

The chip of the controller of memory Champion Memory Address Data Path Controller (MADP) supports 2-Way and 4-Way patterns with memory alternation. Four chips MADP use in 4-Way patterns of the interleaved memory for simplification of multiplexing and data buffering. Single MADP uses for generation of plural copies of the address and check signals in 2-Way interleaved memory patterns.

Input/output controllers

CIOB20

Champion 64-bit/66-MHz PCI System I/O Bridge

Chip Generation Champion PCI System I/O Bridge (CIOB20)) is the second generation of bridges of input/output (CIOB) for PCI.

Provides high-speed link of intermodular bus IMB and two channels PCI.

Effective integrated bus arbiter CIOB20 supports to seven arrangements PCI.

The necessary pass-band is provided with chip CIOB-X supporting operation of 64 bits PCI on frequencies 33, 66 MHz. Queues I/O are besides, realised, provided caching, RAS, etc.

CIOB-X

Grand Champion 100-MHz PCI-X System I/O Bridge

Chip Grand Champion PCI-X System I/O Bridge (CIOB-X) — the high-performance bridge of input/output of systems of a class of firm. Provides high-speed link of intermodular bus IMB and two channels PCI-X. Effective integrated bus arbiter CIOB-X supports to seven arrangements PCI-X. The necessary pass-band is provided with chip CIOB-X supporting operation of 64 bits PCI-X on frequencies 33, 66, 100 MHz. Queues I/O are besides, realised, provided caching, RAS, etc.

CIOB-X2

Grand Champion 133-MHz PCI-X System I/O Bridge

Chip Grand Champion PCI-X System I/O Bridge (CIOB-X2) is the second generation of bridges of input/output (CIOB) for PCI-X. It is intended for systems of a class of firm. Provides high-speed link of intermodular bus IMB and two channels PCI-X. Effective integrated bus arbiter CIOB-X2 supports to seven arrangements PCI-X. The necessary pass-band is provided with chip CIOB-X supporting operation of 64 bits PCI-X on frequencies 33, 66, 100 and 133 MHz. Queues I/O are besides, realised, provided caching, RAS, etc.

CIOB-G2

Grand Champion 8X AGP Workstation Graphics System I/O Bridge

Chip Grand Champion 8X AGP Graphics System I/O Bridge is the second generation of bridges of input/output (CIOB) for graphics subsystems. Provides high-performance path of data between intermodular bus IMB and a drawing subsystem. Supports bus interface AGP for graphics, and also the interface with a memory subsystem through chip GC-WS North Bridge.

CIOB-E

Grand Champion Dual Gigabit Ethernet (Copper) / PCI-X System I/O Bridge

Chip Grand Champion Dual Gigabit Ethernet System I/O Bridge (CIOB-E) is the high-powered bridge for systems of a class of firm. Provides high-speed link of a subsystem of input/output and intermodular bus IMB. Chip CIOB-E contains two Gigabit Ethernet and 64 bits PCI-X (33, 66, 100 MHz).

CIOB-ES

Grand Champion Dual Gigabit Ethernet (SerDes) / PCI-X System I/O Bridge

Chip Grand Champion Dual Gigabit Ethernet (SerDes) System I/O Bridge (CIOB-ES) is the high-powered bridge for systems of a class of firm. Provides high-speed link by a subsystem of input/output and intermodular bus IMB.

Chip CIOB-ES contains double Gigabit Ethernet (MACs), double Gigabit Ethernet on SerDes and to copper wires, 64 bits PCI-X (33, 66, 100 MHz).

Controllers Serial ATA

SWC-IB7452

Dual Channel SATA System I/O Multiplexer

Chip ServerWorks Dual Channel SATA System I/O Multiplexer (SWC-IB7452) is odnochipovyj high-powered double port SATA in SATA or SATA in ATA the bridge. Contains two entering SATA 1.0 ports, and outgoing port which can be konfigurirovan as SATA or ATA. Chip SWC-IB7452 allows usage traditional standard ATA arrangements in the equipment supporting SATA. At the same time gives possibility to apply and arrangements SATA in the same surrounding.

SWC-IB7453

Quad Port SATA System I/O Controller

Chip ServerWorks Quad Port SATA System I/O Controller (SWC-IB7453) is the high-powered controller providing conversion of interfaces of port PCI-X and four ports SATA 1.0.

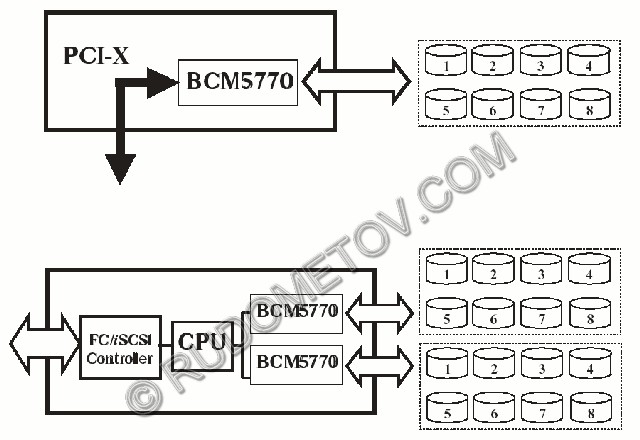

BCM5770R/BCM5770

Quad/Octal-Port SATA/PCI-X Controller

Chips BCM5770 and BCM5770R are vysokointegrirovannymi, multiport controllers SATA I which have been created for the high-performance disk drives which operation is accompanied by low loading of the central processor unit and maximum productivity of a subsystem of input/output.

Controllers are hooked up through 64 bit wire PCI-X 1.0 working on clock rate of 133 MHz. Thus BCM5770R provides handle of four arrangements SATA, and BCM5770 — vosemju with disk drives SATA. Both controllers support "hot" hooking up of arrangements. It gives possibility to insert and delete disk drives SATA, being in a rack of an external memory or in the server block, not interrupting correct system operation.

Fig. 4 Circuit of usage of controllers BCM5770 and BCM5770R in the built in and external subsystems of disk memory

BCM5771

Dual-Port SATA II to SATA II Bridge

Chip BCM5771 — Works Dual Channel SATA System I/O Multiplexer. Represents high-powered odnochipovoe the solution which is carrying out conversion SATA in SATA or SATA in ATA.

Implementators of systems

Servers and the workstations created on the basis of chips ServerWorks and processors of Intel, are well presented in the computer market. Them released and continue to make many known companies. Among them, for example, Dell, Fujitsu-Siemens, HP, IBM, NEC and other corporations which have presented systems of different productivity and a construction (Rack, Blade). These systems are oriented to usage of processors of Intel of Pentium III (DP), Intel of Pentium 4, Intel Xeon DP, Intel Xeon MP and even transportable processors of Intel of Pentium-M.

Perspectives

Perspective processing techniques do not pass by attention of implementators of new models of the chip sets carrying name ServerWorks, and the dedicated components of sets of system logic used in the architecture of multiprocessor servers and powerful workstations.

On the Internet on different sites there were messages on operations of designers on implementation of different innovations, for example, processing techniques of dynamic data compression MXT (Memory eXpansion Technology), developed by IBM. This processing technique urged to increase twice theoretically an informational memory size, not changing its physical size.

There was an information that implementators of chipsets of system logic ServerWorks plan to expand a band of used processors. So, for example, working over the perspective solutions oriented to processors of corporation of Intel, creators of specialised sets do not disregard alternative products. For example, the products intended for solutions, oriented to server processors of company AMD are planned. As it is informed from different sources, 8-processor server systems created on the basis of AMD Opteron prepare for release of a series of chip sets under 1, 2, 4 and even. Predictably, all versions of chip sets will support perspective, high-powered bus PCI Express. And after implementation of the given schedules it is possible to expect release of chip sets ServerWorks for systems on the basis of 16 and 32 processors AMD Opteron.

Article is published in log Byte (http://www.bytemag.ru).

English

English Russian

Russian German

German